Rambus DRAM: Uncovering Facts & Burying Rumors

by Anand Lal Shimpi on May 15, 2000 12:27 AM EST- Posted in

- Memory

The

trend in the computer industry has been towards lowering pin counts. At this

year's Spring IDF, one of the more interesting demonstrations was that of

the Serial ATA specification, which is destined to replace our current ATA

specification, being referred to as Parallel ATA because of the way it transfers

data: multiple bits transferred simultaneously. Since you have multiple bits

of data being transferred simultaneously, you have an enormous pin count,

and when dealing with a large pin count, you have problems of maintaining

signal integrity as the transfer rates increase. Serial ATA will help to

reduce pin count by transferring data one bit at a time but at higher transfer

rates.

The

trend in the computer industry has been towards lowering pin counts. At this

year's Spring IDF, one of the more interesting demonstrations was that of

the Serial ATA specification, which is destined to replace our current ATA

specification, being referred to as Parallel ATA because of the way it transfers

data: multiple bits transferred simultaneously. Since you have multiple bits

of data being transferred simultaneously, you have an enormous pin count,

and when dealing with a large pin count, you have problems of maintaining

signal integrity as the transfer rates increase. Serial ATA will help to

reduce pin count by transferring data one bit at a time but at higher transfer

rates.

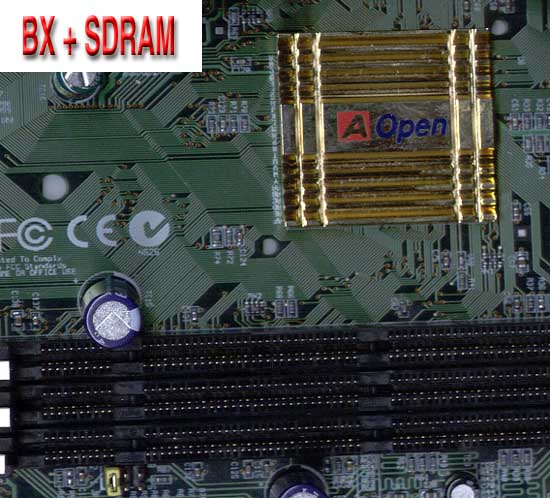

This idea of lowering pin count is mimicked in RDRAM as it transfers data serially, one bit at a time, instead of in a parallel fashion like SDRAM. This, combined with the fact that a single RDRAM channel is only 16-bits wide versus 64-bits for a single SDRAM channel, makes implementing more than one RDRAM channel on a motherboard much easier than implementing more than one SDRAM channel.

The higher your pin count, the more difficult it becomes to route the traces going to your memory banks and your memory controller. Once you reach a certain point you're going to have to start adding more layers to the motherboard's PCB, which begins to increase the cost of the motherboard at a pretty hefty rate. Some motherboard manufacturers such as ABIT won't even consider a motherboard design that employs a design with more than 4 layers; chances are that if you said that an 8-layer design was required in order to have dual SDRAM banks, they would opt for another solution.

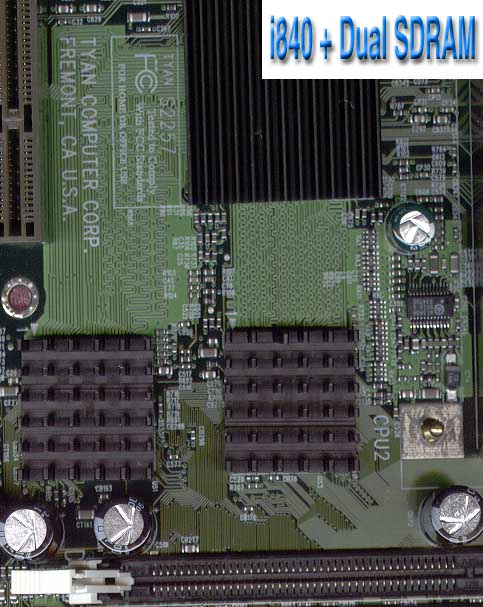

With RDRAM, you can combine two 16-bit RDRAM channels for a total of 3.2GB/s of memory bandwidth without increasing pin count dramatically. In fact, i840 motherboards currently have this dual channel RDRAM system implemented, and although the demand for i840 isn't that great, it is a "living, breathing" example of dual Rambus channels at work. Intel's upcoming Tehama chipset for use with the Willamette will also feature dual Rambus channels, and it shouldn't be much longer before we hear about a higher bandwidth implementation of RDRAM.

Notice the density of the traces present between the North Bridge and the

RIMM slots in comparison to those on the above two examples

1 Comments

View All Comments

dylan522p - Wednesday, December 11, 2013 - link

Wow I wish I read this all those years ago.